SPI 통신설계

SPI 통신

- SPI 통신정의

SPI ( Serial Peripheral Interface ) 통신 : I2C, CAN 과 같은 직렬통신 방식 중 한가지

특징)

1 : N 통신을 지원하는 동기식 통신 방식

동시에 송수신 가능

I2C에 비해 속도가 빠름

하나의 마스터만 지원가능

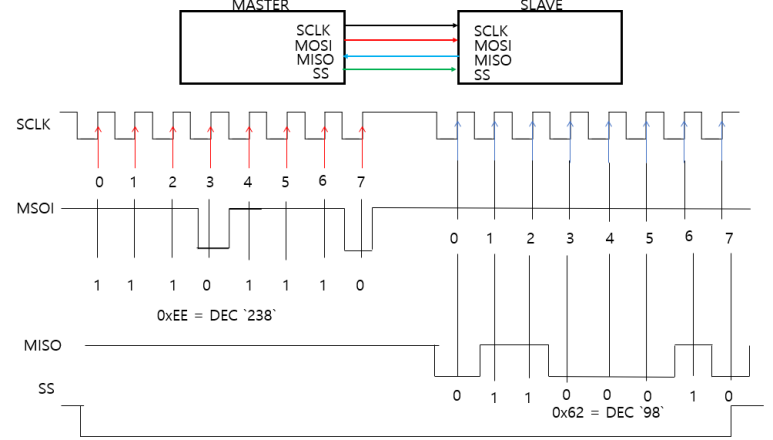

SCLK ( SCK ) : 클럭 동기신호, Master → Slave 전송

MOSI ( Master Output Slave Input ) : Master → Slave 로 데이터 전송

MISO ( Master Input Slave Output ) : 일반적으로 MOSI 를 통해 Slave에 데이터가 입력되면 MISO를 통해 Slave → Maser 로 응답 데이터가 출력

CS ( = SS, Chip Select or Slave Select ) : Master 에서 Slave 를 선택하기 위한 단자.

2. N SPI 통신

1 : N 형태의 SPI 통신의 경우 SCLK 와 SS 를 Master 에서 다양한 방법으로 활용하여 통신이 가능

SPI 통신모드

- CPOL 과 CPHA

CPOL ( Clock Polarity ) : High 또는 Low 설정에 따라 Clock 신호가 발생하지 않을 때의 SLCK의 상태를 결정

CPHA ( Clock Phase ) : 데이터 샘플링 시점을 결정

High 또는 Low 설정에 따라 Data 의 Write / Read 시점을 결정

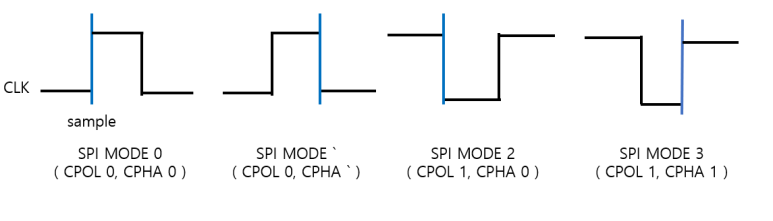

< Mode 0, 1 >

CPOL 이 0 이면 Clock 핀이 Low 상태를 유지하다가 Clock 이 발생되면 Low → High ( Rising edge ) → Low ( Falling edge ) 순서로 클럭을 만든다.

[ Mode 0 ] CPHA 는 데이터를 읽는 타이밍이다. CPHA 가 0 인 경우 상승 ( Rising edge ) 에서 bit 값을 읽고 하강 엣지( Falling edge ) 에서 bit 값을 변경할 수 있다.

[ Mode 1 ] 반대로 CPHA 가 1 이면 하강 엣지에서 bit 값을 변경할 수 있고, 상승 엣지에서 bit 값을 읽는다.

< Mode 2, 3 >

CPOL 이 1 이면 Clock 핀이 High 를 유지하다가 Clock 이 발생되면 High → Low ( Falling edge ) → High ( Rising edge ) 순서로 클럭을 만든다.

[ Mode 2 ] CPHA 는 데이터를 읽는 타이밍이다. CPHA 가 0인 경우 하강 ( Falling edge ) 에서 bit 값을 읽고 상승 엣지 ( Rising edge ) 에서 bit 값을 변경할 수 있다.

[ Mode 3 ] 반대로 CPHA 가 1 이면 상승 엣지에서 bit 값을 변경할 수 있고, 하강 엣지에서 bit 값을 읽는다.

2. SPI 4가지 MODE

CPOL = 0 : 첫 번째 Clock Rising Edge ( Low → High )

CPOL = 1 : 첫 번째 Clock Falling Edge ( High → Low )

CPHA = 0 : 첫 번째 Clock Edge 에서 Data Capture

CPHA = 1 : 두 번째 Clock Edge 에서 Data Capture