반전 증폭기, 비반전 증폭기

반전 증폭기, 비반전 증폭기

1. 반전,비반전을 갖는 연산증폭기란 ?

- 반전, 비반전 증폭기는 연산증폭기 응용에서 가장 유용한 개념들 중의 하나

- 반전,비반전을 이용하여 이득을 안정화시키고 주파수응답을 증가시키기 위해 연산증폭기를 연결할 수 있음

- 반전,비반전은 출력의 일부를 입력의 반대 위상으로 입력에 공급하여 이득이 감소하는 효과를 초래

- 폐루프(closed-loop) 이득은 보통 개루프(open_loop)이득보다 작으며 개루프 이득과는 무관함

2. 폐루프 전압이득, Acl

- 폐루프 전압이득은 피드백 회로에서 전체 회로의 전압 증폭 정도를 나타내는 값

- 회로의 입출력 전압의 비율( Vout / Vin )로 정의되며, 개루프 이득(Open-loop gain)이 아닌, 피드백이 적용된 후의 실제 이득

- 개루프 이득과의 차이 : 개루프 이득은 피드백이 없을 때의 이득으로, 연산 증폭기같은 경우 매우 높은 값을 가지지만, 실제 회로에서 폐루프 이득이 더 중요하려 고려됨

3. 개루프 전압이득, Aol

- 개루프 전압이득(Open-loop Voltage Gain)은 피드백 회로가 없을 때 연산 증폭기(OP Amp)의 출력 전압이 입력 전압에 비해 얼마나 증폭되는지를 나타냄

- 이상적인 경우 무한대이며, 실제 연산 증폭기에서는 매우 큰 수치를 가짐

- 높은 개루프 이득은 피드백 회로를 사용해 안정적이고 정밀한 증폭기(반전 증폭기 등)를 구성하는 데 활용

4. 비반전 증폭기를 사용하는 이유

- 높은 입력 임피던스 : 비반전 증폭기는 입력 신호가 연산 증폭기의 비반전(+) 단자로 직접 들어가고 반전 단자로 전류가 거의 흐르지 않아, 소스에 부담을 주지 않고 신호를 거의 완벽하게 입력받음

- 높은 전압 이득 안정성 : 전압 이득을 안정화시켜 외부 요인에 덜 민감하게 동작

- 낮은 출력 임피던스: 비반전 회로를 통해 출력 임피던스가 낮아지므로, 신호가 부하에 의해 줄어드는 현상(부하 효과)을 줄이고 출력을 효율적으로 전달

- 위상 반전 없음: 출력 신호의 위상이 입력 신호와 동일하여, 입력 신호의 위상이 바뀌지 않음

- 버퍼로서의 역할: 높은 임피던스를 갖는 소스를 낮은 임피던스 회로에 연결할 때, 전압 이득을 1로 설정한 비반전 증폭기(전압 팔로워)를 버퍼로 사용하여 신호 손실 없이 전압을 전달하는 용도로 많이 활용

5. 반전증폭기를 사용하는 이유

- 이득 조절 : 입력과 출력의 전압 이득은 R1 과 R2 의 저항 값 비율 ( - R2 / R1 )로 정밀하게 조절 가능

- 신호 반전 : 입력 신호의 위상을 180° 반전하여 출력. 즉, 입력이 양수이면 음수로, 음수이면 양수로 출력

- 입력 임피던스 조절 : 반전 증폭기의 입력 임피던스는 입력 저항 R1의 값과 같음. 회로에 필요한 입력 임피던스 값을 설계 가능

- 바이어스 전류 오프셋 전압 감소 : 회로의 입력단에 저항을 추가하여 바이어스 전류로 인한 입력 오프셋 전압을 줄이는 데 활용

- 가상 접지 형성 : 비반전 입력 단자가 접지될 때, 반전 증폭기 구조는 반전 입력 단자를 가상 접지(Virtual Ground) 상태로 만듬. 이는 해석 및 설계에 편리한 조건을 제공

- 표는 연산증폭기 동작에 미치는 반전,비반전의 일반적 효과를 요약

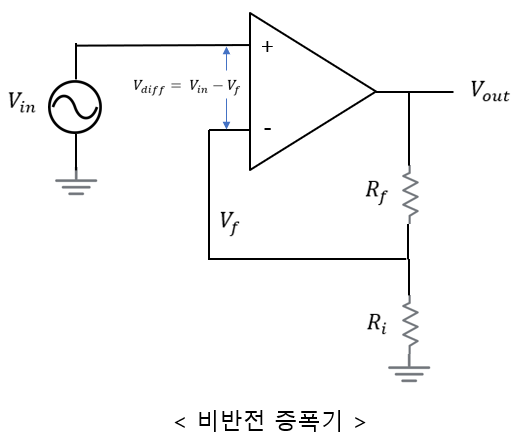

비반전 증폭기 ( Non-inverting Amplifier )

1. 비반전 증폭기

- 연산증폭기를 폐루프(closed-loop)로 구성한 경우, 전압이득을 조절할 수 있는 비반전 증폭기(noninverting amplifier)가 되며 이는 그림과 같음

- 입력신호는 비반전 입력 단자에 인가되며 출력은 Ri 와 Rf로 구성된 귀환회로를 통해 반전 입력 단자로 귀환함

- Ri 와 Rf는 전압분배 회로(voltage divider circuit)를 이루고, 이로 인해 Vout이 감소되며 감소된 Vf 전압을 반전 입력 단자에 연결시킴

- 귀환전압을 식으로 표현하면 다음과 같음

- 입력전압 Vin과 귀환전압 Vf 의 차이는 연산증폭기의 차동 입력과 같음

- 비반전 증폭기의 증폭률은 다음과 같음

폐루프 이득( Acl )은 연산증폭기의 개루프 이득( Aol )에 전혀 의존하지 않으며, 폐루프 이득은 Ri 와 Rf의 값에 의해서만 결정됨

예시) 입력전압 5V , Ri = 10kΩ , Rf = 10kΩ

출처 : Multisim Live Online

2. 전압폴로워 ( Voltage Follower )

- 전압 폴로워(voltage follower)는 그림처럼 모든 출력전압이 반전 입력 단자로 귀환되는 특수한 비반전 증폭기

- 출력이 바로 입력으로 귀환되므로 전압이득은 거의 1

- 비반전 증폭기의 폐루프 전압이득은 1 / B , 전압 폴로워의 귀환율 B = 1이므로 전압 폴로워의 폐루프 이득은

- 전압 폴로워 구성의 가장 중요한 특징은 매우 높은 입력 임피던스, 매우 낮은 출력 임피던스를 가짐

- 이러한 특징으로 전압 폴로워가 거의 이상적인 완충증폭기(buffer amplifier) 역할을 함

3. 비반전 증폭기 사용처

- 버퍼 (Buffer) : 입력 임피던스가 매우 높고 출력 임피던스가 낮은 특성을 이용해, 신호의 손실 없이 단순히 신호를 연결해주는 버퍼로 사용

- 임피던스 매칭 : 저임피던스 부하를 고임피던스 소스에 연결할 때 발생하는 임피던스 불일치를 해결하기 위해 사용

- 증폭기: 입력 신호의 위상을 그대로 유지하면서 신호를 증폭하는 회로로 사용

- 전압 팔로워 (Voltage Follower): 이득이 1인 비반전 증폭기 회로로, 입력 신호를 그대로 출력으로 내보내는 역할을 하며, 이는 버퍼와 유사하게 임피던스를 조절하는 데 사용

적분기: 비반전 구성의 적분기 회로로도 사용

반전 증폭기 ( Inverting Amplifier )

1. 반전증폭기

- 반전 증폭기는 입력 신호의 극성을 반전(반대 위상)시키고, 이득(증폭도)을 조절하여 출력하는 증폭기

그림. a

- 연산증폭기를 사용하여 전압이득이 조절 가능한 반전 증폭기(inverting amplifier)회로를 (그림 a)에 구성

- 입력신호는 직렬 입력 저항 Ri 를 통해 반전(-) 입력 단자에 인가됨

- 출력도 Rf 를 통해 동일 입력 단자로 귀환

- 비반전(+) 입력 단자는 접지에 연결

- 무한대의 입력 임피던스는 반전 입력 단자에 흐르는 전류가 0임을 의미

- 입력 임피던스를 통해 흐르는 전류가 0 이라면, 이때 반전 입력 단자와 비반전 입력 단자 사이의 전압강하는 0

- 이것은 비반전(+) 입력 단자가 접지되었으므로 반전(-) 입력 단자에서의 전압이 0 이라는 것을 의미

그림 b

- 반전 입력 단자에서의 0V 전위를 가상접지(virtual ground)라고 함 (그림 a)

- 반전 입력단자로 유입되는 전류가 0이므로 (그림 b)와 같이 Ri를 통해 흐르는 전류와 Rf를 통해 흐르는 전류는 같음

- 반전 증폭기의 이득은 다음과 같은 식이 된다.

- 위 식으로부터 알 수 있듯이, 반전 증폭기의 폐루프 전압이득(Acl(I))은 저항 Ri에 대한 귀환저항 Rf의 비에 의해 결정됨

- 폐루프 이득은 연산증폭기 내부의 개루프 이득과는 무관하므로 전압이득이 안정적으로 됨

- 여기서 음(-)의 부호는 반전을 나타냄

예시) 입력전압 5V , Ri = 10kΩ , Rf = 10kΩ

출처 : Multisim Live online

2. 반전 증폭기 사용처

- 차동 증폭기: 두 입력 전압의 차이를 증폭하는 데 사용

- 필터: 특정 주파수 대역의 신호만 통과시키거나 차단하는 필터 회로를 구성

- 발진기: 특정 주파수의 신호를 생성하는 발진 회로의 일부로 사용

- 오프셋 보정: 바이어스 전류로 인해 발생하는 출력 전압의 오프셋(기준값 차이)을 줄이는 데 사용

- 신호 왜곡 감소: 특정 연산 증폭기 회로에서 신호 왜곡을 줄이는 용도로 사용